Manual

Login

Our 3D CAD supplier models have been moved to 3Dfindit.com, the new visual search engine for 3D CAD, CAE & BIM models.

You can log in there with your existing account of this site.

The content remains free of charge.

Top Links

Manual

In vielen Situationen ergibt sich die Notwendigkeit, Verbindungen zwischen verschiedenen Klassifikationsentitäten zu modellieren. Dies wird in völlig allgemeiner Form durch die Klasse Inter Part Link modelliert. Sie erlaubt es, zunächst einmal völlig abstrakte Verbindungen zwischen verschiedenen Klasseninstanzen aufzubauen und ist dabei nicht auf ein Part beschränkt. Ein Beispiel dazu wäre ein Schaltschrank mit verschiedenen Klemmen, die durch Kabel miteinander verbunden sind. Die Verbindungsinformation beschreibt in diesem Beispiel die physikalische Verkabelung in abstrakter Weise als logische Verbindung.

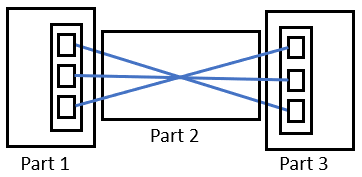

Schematische Darstellung eines Sensorkabels (Stecker - Kabel - Stecker) - Im Allgemeinen werden die beiden Stecker sowie das Kabel eigene Projekte sein. Das System ist in dieser Hinsicht nicht beschränkt.

Die schematische Darstellung aus dem obigen Bild ist für unsere Zwecke nicht vorteilhaft. Deshalb betrachten wir das Beispiel in einer logischen Darstellung. (Analog zu Schaltplänen.)

In dieser logischen Darstellung sind einzelne Eigenschaften der einzelnen Projekte wie Länge, Größe, Breite, Gewicht irrelevant. In diesem Kontext ist das Entscheidende ausschließlich die Verbindungsinformation wie folgende Abbildung demonstriert.

In der höchsten Abstraktionsstufe reduziert sich die Situation zu folgender Tabelle.

| Pin in Part 1 | Verbindung zu Ader (linke Seite) | Verbindung von Ader (rechte Seite) | Pin in Part 2 | |

| 1 | 1 | Kabel | 1 | 3 |

| 2 | 2 | 2 | 2 | |

| 3 | 3 | 3 | 1 |

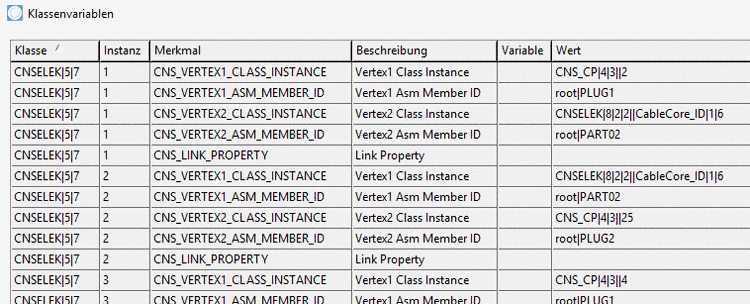

Auf dieser Ebene arbeitet die CNS-Klasse CNSELEK|5|7 (Inter Part Links). Diese Klasse ermöglicht es, auf abstrakter Ebene Verbindungen zwischen allgemeinen Klasseninstanzen aufzubauen (zwei Knoten [Vertex]). Beachte, dass in dem obigen Beispiel die einzelnen Pins Instanzen der Klasse CNS_CP|4|3 (elektrischer Anschluss) sind; die Adern des Kabels sind Instanzen der Klasse CNSELEK|8|2|2 (Kabelader). Aus diesem Grunde enthält die obige Tabelle 6 Verbindungen. D.h. eine Verbindung von den Pins von Part 1 zur linken Seite der Adern sowie Verbindungen von der rechten Seite der Ader zu den Pins von Part 2.

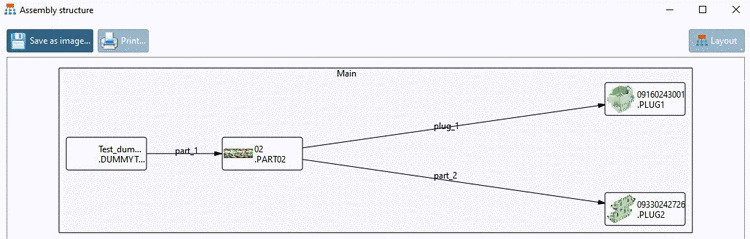

Die Information zu welchen Parts eine einzelne Klasseninstanz gehört wird durch "Aliasse" (eindeutige Bezeichner) gegeben. Man kann sie z.B. im PARTdataManager, im Dialog Assemblystruktur einsehen.

Im Beispielfall gilt: Part 1 hat den Alias "PLUG1", das Kabel hat den Alias "PART02" und für den zweiten Stecker gilt der Alias "PLUG2". Mit diesen "Zutaten" können wir bereits diese Situation modellieren.

Die Klasse CNSELEK|5|7 (Inter Part Link) hat folgende Merkmale:

Vertex 1 ASM Member ID: Lokalisiert das Part (1) der ausgehenden Verbindung über den entsprechenden Alias.

Vertex 1 Class Instance: Lokalisiert die entsprechende Klasseninstanz im Part (1)

Vertex 2 ASM Member ID: Lokalisiert das Part (2) der eingehenden Verbindung über den entsprechenden Alias.

Vertex 2 Class Instance: Lokalisiert die entsprechende Klasseninstanz im Part (2)

Bei den Attributen Vertex Class Instance und Vertex Asm Member ID wird ein analoges Konzept zu XML X-Path verwendet (hier das Pipe-Symbol anstelle des "/"). Einmal um das Part im Assembly zu lokalisieren und dann, um im Part die entsprechende Klasseninstanz festzulegen. Der einzig wichtige Punkt ist, dass das Root-Objekt (Assembly) über den impliziten Alias "root" lokalisiert ist. Die Daten aus der Tabelle nehmen folgende Form an:

Acht Zeilen beschreiben eine komplette Verbindung eines Pins im Stecker 1 mit einem Pin im Stecker 2 via Ader eines Kabels.

Das vorgestellte Schema ist nicht auf Systeme wie Stecker-Kabel-Stecker beschränkt, sondern kann beliebige Verbindungen zwischen Klasseninstanzen in unterschiedlichen Parts beschreiben. Die Bedeutung solcher Konstrukte hängt vom speziellen Fall ab und ist durch die Klasse Inter Part Links zunächst nicht festgelegt.

Bemerkung: Es ist z.B. auch möglich eine Klasseninstanz, die auf dem Assembly selbst "lebt", mit einer Klasseninstanz eines Parts zu verbinden; dies würde wie folgt aussehen:

Subcircuits folgen direkt der oben dargestellten allgemeinen Vorgehensweise. Um allerdings einen expliziten Subcircuit zu erstellen, muss auf Ebene des Assemblies noch die Klasse CNSELEK|1, mit dem Merkmal Override Component Type, mit dem Wert "SubCircuit" geschrieben werden. Dies setzt eine konsistente Modellierung der Inter Part Links voraus.